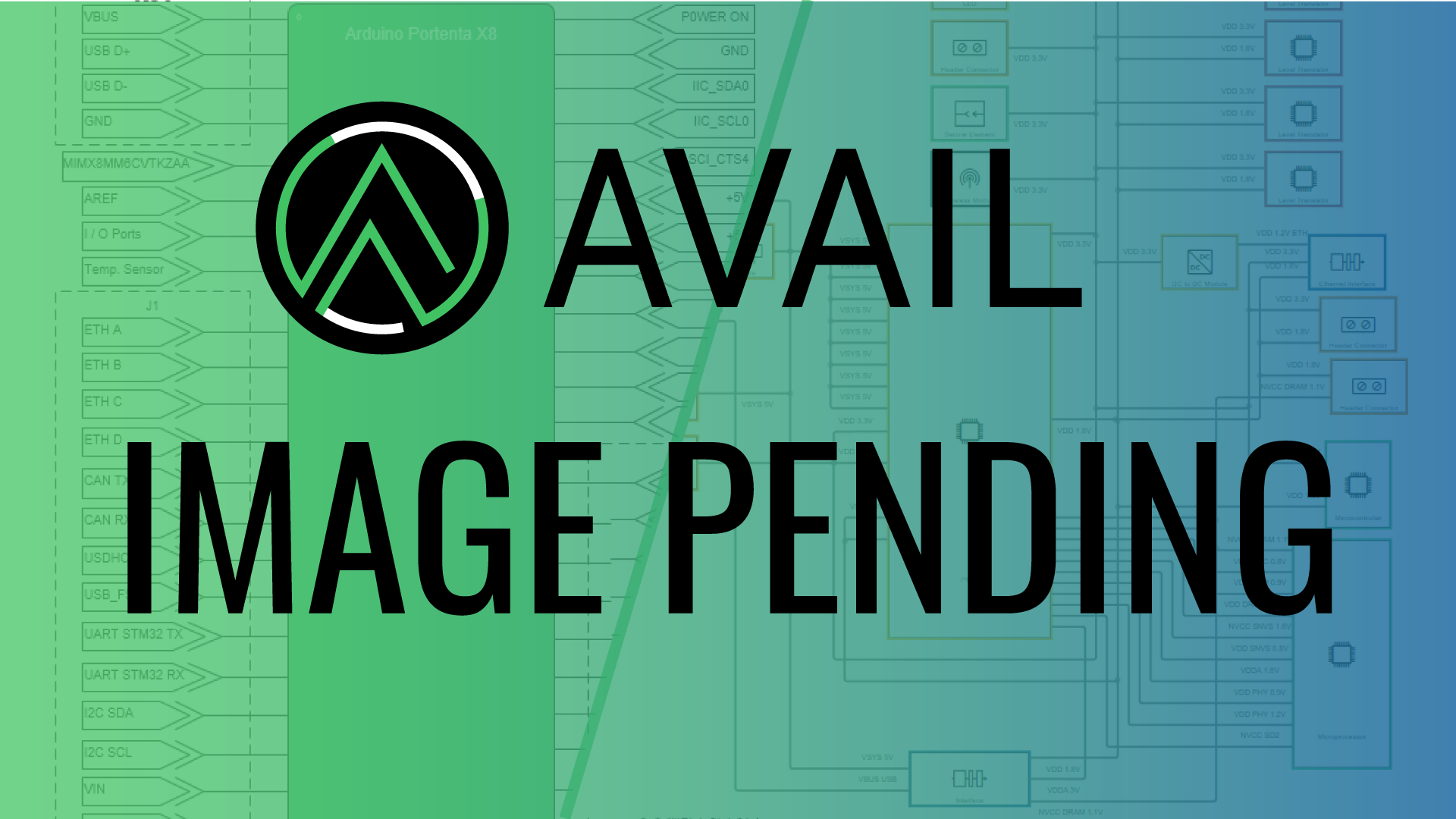

Gen5 PCIe Switches Block Diagram based on Broadcom Solution

Would you like this design to be modifiable in the future?

Grayed out parts are unavailable for purchase on Avnet Silica.

The displayed part lists is a small subset of the complete BOM.

| MFGR | PART# | BLK NM |

|---|

IMPORTANT NOTICE AND DISCLAIMER: AVNET PROVIDES THESE DESIGN FILES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY. SEE LEGAL NOTICES | AVNET EMEA FOR ADDITIONAL INFORMATION.